# LE866 PSM APPLICATION NOTE

80471NT11483A Rev.1 2016-12-22

# **APPLICABILITY TABLE**

#### **PRODUCTS**

- LE866-SV1

- LE866A1-KK

- ■■ LE866A1-NA

- **LE866A1-JS**

## **DISCLAIMER**

#### **LEGAL NOTICE**

These Specifications are general guidelines pertaining to product selection and application and may not be appropriate for your particular project. Telit (which hereinafter shall include, its agents, licensors and affiliated companies) makes no representation as to the particular products identified in this document and makes no endorsement of any product. Telit disclaims any warranties, expressed or implied, relating to these specifications, including without limitation, warranties or merchantability, fitness for a particular purpose or satisfactory quality. Without limitation, Telit reserves the right to make changes to any products described herein and to remove any product, without notice.

It is possible that this document may contain references to, or information about Telit products, services and programs, that are not available in your region. Such references or information must not be construed to mean that Telit intends to make available such products, services and programs in your area.

#### **USE AND INTELLECTUAL PROPERTY RIGHTS**

These Specifications (and the products and services contained herein) are proprietary to Telit and its licensors and constitute the intellectual property of Telit (and its licensors). All title and intellectual property rights in and to the Specifications (and the products and services contained herein) is owned exclusively by Telit and its licensors. Other than as expressly set forth herein, no license or other rights in or to the Specifications and intellectual property rights related thereto are granted to you. Nothing in these Specifications shall, or shall be deemed to, convey license or any other right under Telit's patents, copyright, mask work or other intellectual property rights or the rights of others.

You may not, without the express written permission of Telit: (i) copy, reproduce, create derivative works of, reverse engineer, disassemble, decompile, distribute, merge or modify in any manner these Specifications or the products and components described herein; (ii) separate any component part of the products described herein, or separately use any component part thereof on any equipment, machinery, hardware or system; (iii) remove or destroy any proprietary marking or legends placed upon or contained within the products or their components or these Specifications; (iv) develop methods to enable unauthorized parties to use the products or their components; and (v) attempt to reconstruct or discover any source code, underlying ideas, algorithms, file formats or programming or interoperability interfaces of the products or their components by any means whatsoever. No part of these Specifications or any products or components described herein may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, without the prior express written permission of Telit.

#### **HIGH RISK MATERIALS**

Components, units, or third-party products contained or used with the products described herein are NOT fault-tolerant and are NOT designed, manufactured, or intended for use as on-line control equipment in the following hazardous environments requiring fail-safe controls: the operation of Nuclear Facilities, Aircraft Navigation or Aircraft Communication Systems, Air Traffic Control, Life Support, or Weapons Systems ("High Risk Activities"). Telit, its licensors and its supplier(s) specifically disclaim any expressed or implied warranty of fitness for such High Risk Activities.

#### **TRADEMARKS**

You may not and may not allow others to use Telit or its third party licensors' trademarks. To the extent that any portion of the products, components and any accompanying documents contain proprietary and confidential notices or legends, you will not remove such notices or legends.

#### THIRD PARTY RIGHTS

The software may include Third Party Right software. In this case you agree to comply with all terms and conditions imposed on you in respect of such separate software. In addition to Third Party Terms, the disclaimer of warranty and limitation of liability provisions in this License shall apply to the Third Party Right software.

TELIT HEREBY DISCLAIMS ANY AND ALL WARRANTIES EXPRESS OR IMPLIED FROM ANY THIRD PARTIES REGARDING ANY SEPARATE FILES, ANY THIRD PARTY MATERIALS INCLUDED IN THE SOFTWARE, ANY THIRD PARTY MATERIALS FROM WHICH THE SOFTWARE IS DERIVED (COLLECTIVELY "OTHER CODE"), AND THE USE OF ANY OR ALL THE OTHER CODE IN CONNECTION WITH THE SOFTWARE, INCLUDING (WITHOUT LIMITATION) ANY WARRANTIES OF SATISFACTORY QUALITY OR FITNESS FOR A PARTICULAR PURPOSE.

NO THIRD PARTY LICENSORS OF OTHER CODE SHALL HAVE ANY LIABILITY FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING WITHOUT LIMITATION LOST PROFITS), HOWEVER CAUSED AND WHETHER MADE UNDER CONTRACT, TORT OR OTHER LEGAL THEORY, ARISING IN ANY WAY OUT OF THE USE OR DISTRIBUTION OF THE OTHER CODE OR THE EXERCISE OF ANY RIGHTS GRANTED UNDER EITHER OR BOTH THIS LICENSE AND THE LEGAL TERMS APPLICABLE TO ANY SEPARATE FILES, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Copyright © Telit Communications PLC.

# **CONTENTS**

| 1           | Introduction                             | 6             |

|-------------|------------------------------------------|---------------|

| 1.1         | Scope                                    | 6             |

| 1.2         | Audience                                 | 6             |

| 1.3         | Contact Information, Support             | 6             |

| 1.4         | List of acronyms                         | 7             |

| 1.5         | Text Conventions                         | 8             |

| 1.6.        | Related Documents                        | 8             |

| 2<br>3<br>4 | Overview PSM Description Pins Allocation | 9<br>10<br>11 |

| 4.1         | PIN list for PSM Mode                    | 11            |

| 4.2         | LGA Pads Layout                          | 13            |

| 4.3         | PSM SIGNALS DETAIL                       | 14            |

| 4.3.1       | PSM_WAKE                                 | 14            |

| 4.3.2       | PSM_STATUS                               | 14            |

| 4.3.3       | PSM_ENA_OUT                              | 14            |

| 4.3.4       | RESET*                                   | 14            |

| 4.3.5       | VDDIO_IN                                 | 14            |

| 4.4         | Logic Levels Specification               | 15            |

| 4.5         | General Design Rules                     | 16            |

| 4.5.1       | Power Supply Guidelines                  | 16            |

| 4.5.2       | Digital IOs Supply Guidelines            | 17            |

| 4.5.3       | SIM Lines control                        | 19            |

| 4.6         | Enter and Exit from PSM States           | 20            |

| 5           | Document History                         | 22            |

| 5.1         | Revisions                                | 22            |

# 1 INTRODUCTION

## 1.1 Scope

The LE866 includes unique advanced features in order to support the PSM according to 3GPP Rel-12. The aim of this document is the description of the suggested Application design to use this functionality.

### 1.2 Audience

This document is intended for Telit customers, who are integrators, about to implement their applications using our LE866 modules.

## 1.3 Contact Information, Support

For general contact, technical support services, technical questions and report documentation errors contact Telit Technical Support at:

TS-EMEA@telit.com

TS-AMERICAS@telit.com

TS-APAC@telit.com

Alternatively, use:

http://www.telit.com/support

For detailed information about where you can buy the Telit modules or for recommendations on accessories and components visit:

http://www.telit.com

Our aim is to make this guide as helpful as possible. Keep us informed of your comments and suggestions for improvements.

Telit appreciates feedback from the users of our information.

# 1.4 List of acronyms

| Acronym | Description                                |  |

|---------|--------------------------------------------|--|

| TTSC    | Telit Technical Support Centre             |  |

| USB     | Universal Serial Bus                       |  |

| HS      | High Speed                                 |  |

| DTE     | Data Terminal Equipment                    |  |

| LTE     | Long Term Evolution                        |  |

| PSM     | Power Saving Mode according to 3GPP Rel.12 |  |

| AS      | Access Stratum                             |  |

| NAS     | Non-Access Stratum                         |  |

| RAU     | Routing Area Update                        |  |

| TAU     | Tracking Area Update                       |  |

| HSIC    | High Speed Inter Chip                      |  |

| SIM     | Subscriber Identification Module           |  |

| SPI     | Serial Peripheral Interface                |  |

| ADC     | Analog – Digital Converter                 |  |

| DAC     | Digital – Analog Converter                 |  |

| I/O     | Input Output                               |  |

| GPIO    | General Purpose Input Output               |  |

| CMOS    | Complementary Metal – Oxide Semiconductor  |  |

| CLK     | Clock                                      |  |

| MRDY    | Master Ready                               |  |

| SRDY    | Slave Ready                                |  |

| CS      | Chip Select                                |  |

| RTC     | Real Time Clock                            |  |

| PCB     | Printed Circuit Board                      |  |

| ESR     | Equivalent Series Resistance               |  |

| VSWR    | Voltage Standing Wave Radio                |  |

| VNA     | Vector Network Analyzer                    |  |

|         |                                            |  |

## 1.5 Text Conventions

Danger – This information MUST be followed or catastrophic equipment failure or bodily injury may occur.

Caution or Warning – Alerts the user to important points about integrating the module, if these points are not followed, the module and end user equipment may fail or malfunction.

Tip or Information – Provides advice and suggestions that may be useful when integrating the module.

All dates are in ISO 8601 format, i.e. YYYY-MM-DD.

### 1.6. Related Documents

- LE866 HW User Guide

- LE866 AT Commands Reference Guide

- Telit EVK2 User Guide

1VV0301210 80471ST10691A 1vv0300704

## 2 OVERVIEW

The aim of this document is the description of some hardware solutions useful for developing a product with the Telit LE866 module.

In this document all the basic functions of a mobile phone will be taken into account; for each one of them a proper hardware solution will be suggested and eventually the wrong solutions and common errors to be avoided will be evidenced. Obviously this document cannot embrace the whole hardware solutions and products that may be designed. The wrong solutions to be avoided shall be considered as mandatory, while the suggested hardware configurations shall not be considered mandatory, instead the information given shall be used as a guide and a starting point for properly developing your product with the Telit LE866 module. For further hardware details that may not be explained in this document refer to the Telit LE866 Product Description document where all the hardware information is reported.

#### NOTICE:

- (EN) The integration of the LTE **LE866** cellular module within user application shall be done according to the design rules described in this manual.

- (IT) L'integrazione del modulo cellulare LTE **LE866** all'interno dell'applicazione dell'utente dovrà rispettare le indicazioni progettuali descritte in questo manuale.

- (DE) Die Integration des **LE866** LTE Mobilfunk-Moduls in ein Gerät muß gemäß der in diesem Dokument beschriebenen Kunstruktionsregeln erfolgen.

- (SL) Integracija LTE **LE866** modula v uporabniški aplikaciji bo morala upoštevati projektna navodila, opisana v tem priročniku.

- (SP) La utilización del modulo LTE **LE866** debe ser conforme a los usos para los cuales ha sido deseñado descritos en este manual del usuario.

- (FR) L'intégration du module cellulaire LTE **LE866** dans l'application de l'utilisateur sera faite selon les règles de conception décrites dans ce manuel.

- (HE) האינטגרטור מתבקש ליישם את ההנחיות המפורטות במסמך זה בתהליך האינטגרציה של המודם הסלולרי (HE) עם המוצר.

The information presented in this document is believed to be accurate and reliable. However, no responsibility is assumed by Telit Communications S.p.A. for its use, nor any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of Telit Communications S.p.A. other than for circuitry embodied in Telit products. This document is subject to change without notice.

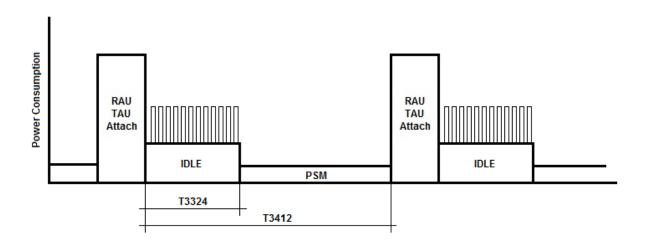

## 3 PSM DESCRIPTION

The Power Saving Mode (PSM) in 3GPP Rel12 allows the Module to skip idle mode tasks for a longer time period while still maintaining the NAS context.

This feature permits to reduce the overall power consumption when there is no required data activity with the network for a long time.

This saves the power also related to the Paging activity.

The PSM reduces the signaling load between the LE866 and the network on NAS level (24.301 Rel.12 chapter 5.3.11) compared to a standard attach/detach procedure.

Within the attach/RAU/TAU procedure the UE indicates that it supports PSM.

The network confirms PSM usage by sending a value for a timer (T3324) in the confirmation message.

The timer T3324 specifies an active period after the RAU/TAU procedure the UE has to follow the normal idle mode procedures (paging reception, measurements,..).

After timer T3324 elapses the Module enters PSM state, i.e. it disables all AS/NAS activities until the next periodic RAU/TAU update.

A second Timer (T3412) is defining the duration of the PSM.

During this period the Module is NOT reachable by the network, i.e. it cannot be paged and stops access stratum activities.

Before the inactivity period the complete NAS context needs to be stored and reused when accessing the network again.

The Module can leave the PSM mode at any point in time when there is MO data or when periodic TAU timer expires.

The PSM is only intended for those Modules that can tolerate a high MT Call latency.

The 3GPP standard does not imply whether or to which extend the PSM does reduce the power of the Module. Only the signaling reduction (i.e. Not doing a reattach but just a RAU/TAU procedure) is defined.

# 4 PINS ALLOCATION

## 4.1 PIN list for PSM Mode

| Pin               | Signal             | I/O | Function                                       | Туре      | Comment                      |

|-------------------|--------------------|-----|------------------------------------------------|-----------|------------------------------|

| PSM Control Lines |                    |     |                                                |           |                              |

| D3                | PSM_WAKE           | 1   | Wake Up from PSM Mode                          | Analog    |                              |

| E8                | PSM_STATUS         | 0   | PSM Status                                     | CMOS 1.8V |                              |

| F8                | PSM_ENA_OUT        | 0   | PSM Enable for external LDOs                   | CMOS 1.8V |                              |

| SIM ca            | ard interface      |     |                                                |           |                              |

| <b>C</b> 7        | SIMVCC             | -   | External SIM signal – Power supply for the SIM | 1.8V Only |                              |

| В7                | SIMRST             | 0   | External SIM signal – Reset                    | CMOS 1.8  |                              |

| A7                | SIMCLK             | 0   | External SIM signal – Clock                    | CMOS 1.8  |                              |

| A6                | SIMIO              | I/O | External SIM signal – Data I/O                 | CMOS 1.8  |                              |

| D8                | VDDIO_IN           | 1   | IO bus Supply input                            | Power     |                              |

| RF SE             | CTION              |     |                                                |           |                              |

| G2                | MAIN_ANT           | I/O | LTE Main Antenna (50 ohm)                      | RF        |                              |

| C0                | DIV_ANT            | 1   | LTE RX Diversity Antenna (50 ohm)              | RF        |                              |

| Miscel            | llaneous Functions |     |                                                |           |                              |

| G4                | RESET*             | 1   | Reset Input                                    | VBATT     | Pull up to VBATT<br>(10Kohm) |

| G6                | VAUX<br>PWRMON     | 0   | 1.8V stabilized output<br>Power ON monitor     | Power     |                              |

| Power             | Supply             |     |                                                |           |                              |

| E2                | VBATT              | -   | Main power supply (Baseband)                   | Power     |                              |

| E0                | VBATT_PA           | -   | Main power supply (Radio PA)                   | Power     |                              |

| E1                | VBATT_PA           | -   | Main power supply (Radio PA)                   | Power     |                              |

| В0                | GND                | -   | Ground                                         | Power     |                              |

| D0                | GND                | -   | Ground                                         | Power     |                              |

| F0                | GND                | -   | Ground                                         | Power     |                              |

| G0                | GND                | -   | Ground                                         | Power     |                              |

| D1                | GND                | -   | Ground                                         | Power     |                              |

| F1                | GND                | -   | Ground                                         | Power     |                              |

| G1                | GND                | -   | Ground                                         | Power     |                              |

| D2        | GND | - | Ground | Power |

|-----------|-----|---|--------|-------|

| F2        | GND | - | Ground | Power |

| C3        | GND | - | Ground | Power |

| E3        | GND | - | Ground | Power |

| F3        | GND | - | Ground | Power |

| G3        | GND | - | Ground | Power |

| F6        | GND | - | Ground | Power |

| <b>A8</b> | GND | - | Ground | Power |

| G8        | GND | - | Ground | Power |

| A11       | GND | - | Ground | Power |

| G11       | GND | - | Ground | Power |

# 4.2 LGA Pads Layout

#### **TOP VIEW**

|    | TOP VIEW |           |            |              |                |                 |                 |

|----|----------|-----------|------------|--------------|----------------|-----------------|-----------------|

|    | Α        | В         | С          | D            | Е              | F               | G               |

| 0  | RESERVED | GND       | DIV<br>ANT | GND          | VBATT_PA       | GND             | GND             |

| 1  | C105/RTS | C106/CTS  | TX AUX     | GND          | VBATT_PA       | GND             | GND             |

| 2  | C108/DTR | C109/DCD  | RX AUX     | GND          | VBATT          | GND             | MAIN<br>ANT     |

| 3  | C107/DSR | C125/RING | GND        | PSM_WAK<br>E | GND            | GND             | GND             |

| 4  | C103/TXD | GPIO_06   | GPIO_07    | RESERVED     | DAC_OUT        | ADC_IN1         | RESET*          |

| 5  | C104/RXD | GPIO_05   | GPIO_01    | GPIO_04      | USB_D+         | RESERVED        | RESERVED        |

| 6  | SIMIO    | RESERVED  | GPIO_02    | GPIO_03      | USB_D-         | GND             | VAUX/PWR<br>MON |

| 7  | SIMCLK   | SIMRST    | SIMVCC     | RESERVED     | RESERVED       | RESERVED        | RESERVED        |

| 8  | GND      | RESERVED  | RESERVED   | VDDIO_IN     | PSM_STAT<br>US | PSM_ENA_<br>OUT | GND             |

| 9  | RESERVED | RESERVED  | RESERVED   | RESERVED     | RESERVED       | RESERVED        | RESERVED        |

| 10 | RESERVED | RESERVED  | RESERVED   | RESERVED     | RESERVED       | RESERVED        | RESERVED        |

| 11 | GND      | RESERVED  | RESERVED   | RESERVED     | RESERVED       | RESERVED        | GND             |

### 4.3 PSM SIGNALS DETAIL

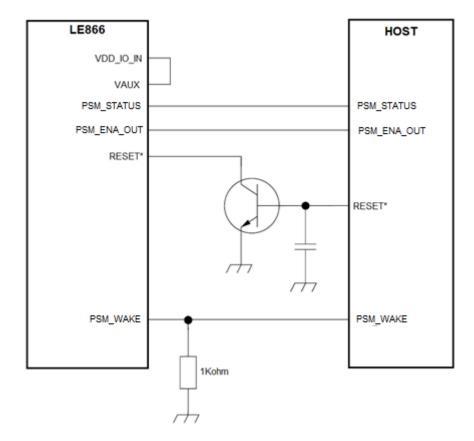

#### 4.3.1 PSM WAKE

PSM\_WAKE is the only pin that can wake the system from the PSM Mode.

It is normally Low and should be set to High to wake up the module.

#### NOTE:

The pin requires to add a pull down resistor on the application.

#### 4.3.2 PSM\_STATUS

PSM\_STATUS is a GPIO controlled by SW that is low during the PSM mode and high during regular operation. This pin is used for the LE866/Host Controller protocol when entering/exiting PSM state.

#### 4.3.3 PSM\_ENA\_OUT

PSM\_ENA\_OUT is low during normal operation and open drain during the PSM state. It may be used to enable/disable the unnecessary supplies to the different system components when entering exiting the PSM state.

#### 4.3.4 RESET\*

RESET\* disables the entire integrated power management and is used as a power reset.

#### 4.3.5 VDDIO\_IN

VDDIO\_IN is the Digital IO supply Input pin.

## 4.4 Logic Levels Specification

#### **ABSOLUTE MAXIMUM RATINGS:**

| Parameter                                                                                   | Min   | Max               |

|---------------------------------------------------------------------------------------------|-------|-------------------|

| Input level on any digital pin (CMOS 1.8) with respect to ground                            | -0.3V | VDDIO_IN<br>+0.3V |

| Input level on any digital pin (CMOS 1.8) with respect to ground when VDDIO is not supplied | -0.3V | 0.3V              |

### **OPERATING RANGE - INTERFACE LEVELS (1.8V CMOS):**

| Parameter         | Min   | Max   |

|-------------------|-------|-------|

| Input high level  | 1.55V | 1.9V  |

| Input low level   | 0V    | 0.35V |

| Output high level | 1.35V | 1.8V  |

| Output low level  | 0V    | 0.8V  |

#### NOTE:

If VDDIO\_IN line is not powered (i.e. during the sleep states in PSM=2 when supplied by VAUX, during transition phases BOOT, RESET etc. and when the module is unsupplied) it is important to avoid back powering the digital pins. Exceeding the absolute maximum ratings could damage permanently the module.

# 4.5 General Design Rules

The principal guidelines for the PSM Design embrace three different design steps:

- the Power supply

- the Digital IOs supply and control

- the SIM Interface latches.

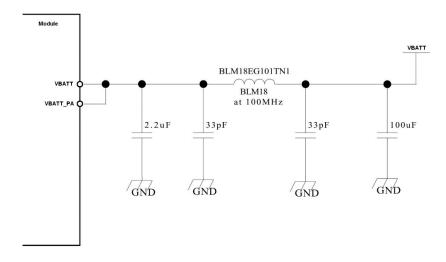

### 4.5.1 Power Supply Guidelines

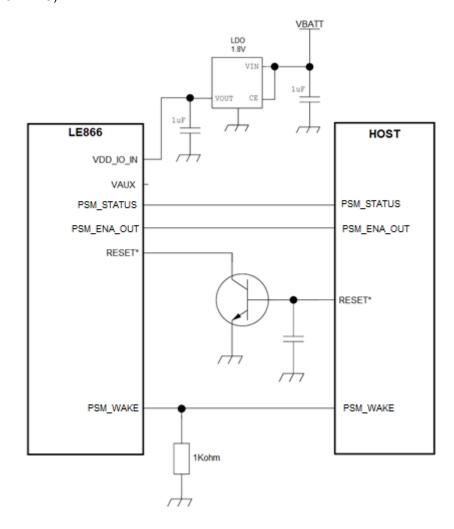

The below figure shows the recommended circuit:

For additional details please refer to the LE866 HW User Guide

#### 4.5.2 Digital IOs Supply Guidelines

The Digital IO section requires to be supplied applying a 1.8V power supply to the VDDIO\_IN input. In a normal Application design, this is done connecting the VDDIO\_IN to the VAUX/PWRMON line. Using this supply line we have two effects:

- When in PSM=2 the VAUX is switched off so the Host has to ensure to avoid applying any high logic level to the IOs that could damage the module.

- VAUX has a quiescent current of ~40uA and if it is kept alive also VSIM is kept alive (total of ~80uA)

During the PSM modes the host should ignore the value of the signals coming from the LE866 (as all pins are turned to High Z if VDD\_IO\_IN is available or to non defined state if VDDIO\_IN is shut off)

In systems that cannot ensure that no voltage will be applied to the LE866 IOs during PSM status, the VDDIO\_IN line should be kept supplied.

The LE866 lowest power consumption can be achieved powering the VDDIO\_IN externally (allowing all other LE866 power supplies to be disabled).

This could be done using for example an LDO with a low quiescent current (i.e. TOREX XC6504A181NR-G)

Another alternative is to add logic such as a buffer on the required signals, using the PSM\_STATUS line as the output enable control Low=PSM, High=Not PSM.

### 4.5.3 SIM Lines control

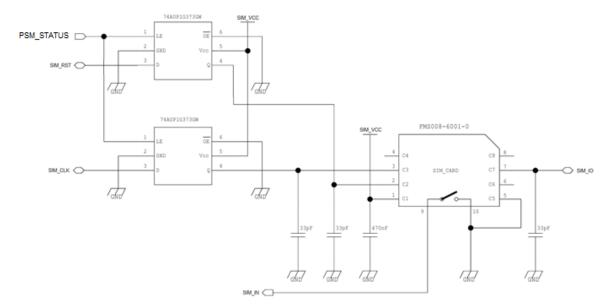

In order to ensure the 3GPP Rel.12 compliance when using the SIM in PSM states it is suggested to use two latches on the SIM\_RST and SIM\_CLK lines.

The two latches are enabled by the PSM\_STATUS line.

### 4.6 Enter and Exit from PSM States

Since the LE866 outputs become inputs\non-defined during the PSM states, the module and the host should follow a specific protocol to ensure the proper system operation:

- LE866 notifies the host before going into a PSM state by setting PSM\_STATUS low

- Host makes proper preparations and notifies the LE866 he is allowed to enter the PSM state by setting the PSM\_WAKE low (this could be avoided if a pull down resistor is added to the PSM\_WAKE line)

- LE866 enters in PSM state

- If required, the host can wake the LE866 at any time by setting the PSM\_WAKE line high.

- LE866 notifies the host when it is out of the PSM states by setting PSM\_STATUS high

- Host keeps the PSM\_WAKE line high to ensure the module does not enter the PSM states without proper coordination and permission from the host.

If required on specific applications or by specific hosts, it is possible to add dedicated external logic to toggle the PSM\_WAKE pin high, when there is an event on the preferred pin/interface (for example on the UART RTS)

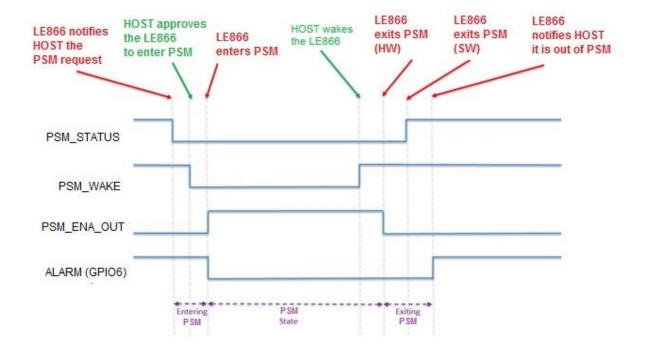

The following diagram shows the process of PSM enter/exit due to Host request:

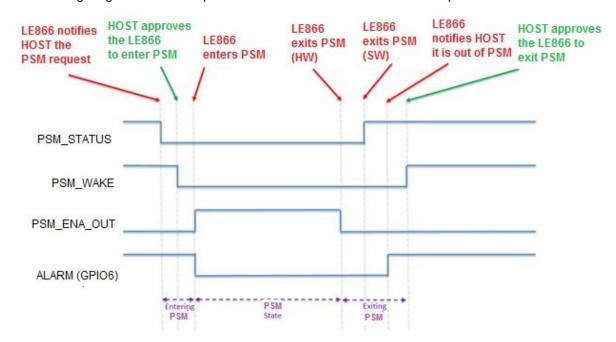

The following diagram shows the process of PSM enter/exit due to RTC request:

# 5 DOCUMENT HISTORY

## 5.1 Revisions

| Revision | Date       | Changes                      |

|----------|------------|------------------------------|

| 0        | 2016-07-26 | Preliminary Version          |

| 1        | 2016-12-22 | Updated 1.4, 4.3, 4.4, 4.5.2 |

|          |            |                              |

|          |            |                              |